# RTL8251C-GR RTL8251CL-GR

# INTEGRATED 10/100/1000 GIGABIT ETHERNET TRANSCEIVER

# **DATASHEET** (CONFIDENTIAL: Development Partners Only)

Rev. 1.2 05 August 2010 Track ID: JATR-2265-11

Realtek Semiconductor Corp. No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan Tel.: +886-3-578-0211 Fax: +886-3-577-6047 www.realtek.com

#### COPYRIGHT

©2010 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp.

#### DISCLAIMER

Realtek provides this document "as is", without warranty of any kind. Realtek may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.

#### TRADEMARKS

Realtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.

#### **USING THIS DOCUMENT**

This document is intended for the software engineer's reference and provides detailed programming information.

Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide.

#### **REVISION HISTORY**

| Revision | <b>Release Date</b> | Summary                                             |  |  |

|----------|---------------------|-----------------------------------------------------|--|--|

| 1.0      | 2008/09/10          | First release.                                      |  |  |

| 1.1      | 2009/08/11          | Revised section 8 Switching Regulator, page 34.     |  |  |

|          |                     | Revised section 8.1 PCB Layout, page 34.            |  |  |

|          |                     | Revised section 10.5.2 RGMII Timing Modes, page 45. |  |  |

| 1.2      | 2010/08/05          | Removed CLK125 feature.                             |  |  |

ii

# **Table of Contents**

| 1. | GEN          | ERAL DESCRIPTION                        | 1 |

|----|--------------|-----------------------------------------|---|

| 2. | FEA          | TURES                                   | 2 |

| 2. |              |                                         |   |

| 3. | SYS          | FEM APPLICATIONS                        | 2 |

| 4. | PIN          | ASSIGNMENTS                             | 3 |

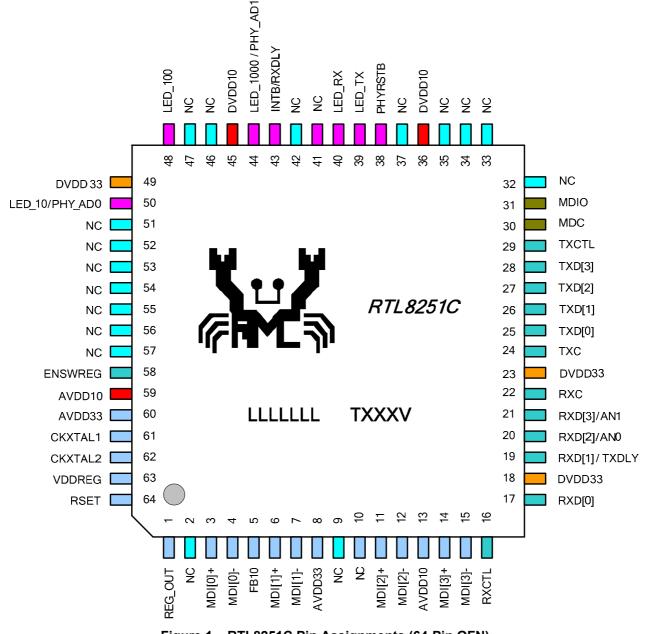

| т. |              | RTL8251C Pin Assignments (64-Pin QFN)   |   |

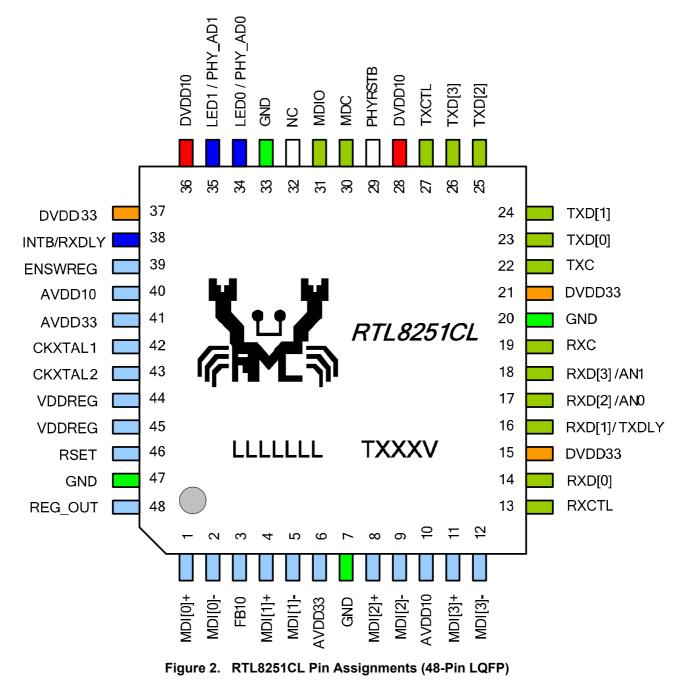

|    | 4.1.         |                                         |   |

|    | 4.2.<br>4.3. | PACKAGE IDENTIFICATION                  |   |

|    | 4.5.<br>4.4. | PACKAGE IDENTIFICATION                  |   |

|    |              |                                         |   |

| 5. | PIN          | DESCRIPTIONS                            | 5 |

|    | 5.1.         | TRANSCEIVER INTERFACE                   | 5 |

|    | 5.2.         | СLOCК                                   | 5 |

|    | 5.3.         | RGMII                                   | 6 |

|    | 5.4.         | MANAGEMENT INTERFACE                    | 6 |

|    | 5.5.         | RESET                                   |   |

|    | 5.6.         | MODE SELECTION                          | 7 |

|    | 5.7.         | LED INDICATION                          |   |

|    | 5.8.         | REGULATOR AND REFERENCE                 |   |

|    | 5.9.         | POWER AND GROUND                        | 8 |

|    | 5.10.        | NOT CONNECTED                           | 8 |

| 6. | FUN          | CTION DESCRIPTION                       | 9 |

|    | 6.1.         | TRANSMITTER                             | ٥ |

|    | 6.1.1        |                                         |   |

|    | 6.1.2        |                                         |   |

|    | 6.1.3        |                                         |   |

|    | 6.2.         | RECEIVER                                |   |

|    | 6.2.1        |                                         |   |

|    | 6.2.2        |                                         |   |

|    | 6.2.3        |                                         |   |

|    | 6.3.         | HARDWARE CONFIGURATION                  |   |

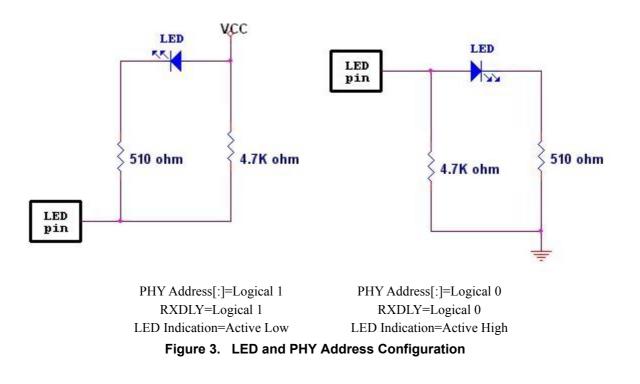

|    | 6.4.         | LED AND PHY ADDRESS CONFIGURATION       |   |

|    | 6.5.         | MAC/PHY INTERFACE                       |   |

|    |              | . RGMII                                 |   |

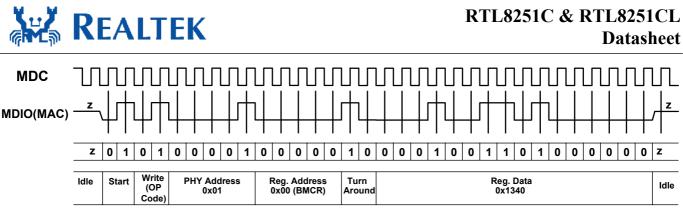

|    |              | Management Interface                    |   |

|    | 6.6.         | AUTO-NEGOTIATION                        |   |

|    | 6.6.1        |                                         |   |

|    | 6.6.2        |                                         |   |

|    | 6.6.3        |                                         |   |

|    | 6.7.         | CROSSOVER DETECTION AND AUTO-CORRECTION |   |

|    | 6.8.         | LED CONFIGURATION                       |   |

|    | 6.8.1        |                                         |   |

|    | 6.8.2        | 20                                      |   |

|    | 6.9.         | POLARITY CORRECTION                     |   |

|    | 6.10.        | POWER                                   |   |

|    |              |                                         |   |

iii

| 7. REGISTER DESCRIPTIONS                                                                                                      |    |

|-------------------------------------------------------------------------------------------------------------------------------|----|

| 7.1. REGISTER MAPPING AND DEFINITIONS                                                                                         | 22 |

| 7.2. REGISTER TABLE                                                                                                           |    |

| 7.2.1. BMCR (Basic Mode Control Register, Address 0x00)                                                                       |    |

| 7.2.2. BMSR (Basic Mode Status Register, Address 0x01)                                                                        |    |

| 7.2.3. PHYID1 (PHY Identifier Register 1, Address 0x02)                                                                       |    |

| 7.2.4. PHYID2 (PHY Identifier Register 2, Address 0x03)                                                                       |    |

| 7.2.5. ANAR (Auto-Negotiation Advertising Register, Address 0x04)                                                             |    |

| 7.2.6. ANLPAR (Auto-Negotiation Link Partner Ability Register, Address 0                                                      |    |

| 7.2.7. ANER (Auto-Negotiation Expansion Register, Address 0x06)                                                               |    |

| 7.2.8. ANNPTR (Auto-Negotiation Next Page Transmit Register, Address 0                                                        |    |

| 7.2.9. ANNPRR (Auto-Negotiation Next Page Receive Register, Address 0x                                                        |    |

| 7.3. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x09)                                                                         |    |

| 7.3.1. GBSR (1000Base-T Status Register, Address 0x0A)                                                                        |    |

| 7.3.2. GBESR (1000Base-T Extended Status Register, Address 0x0F)                                                              |    |

| 7.3.3. PHYCR (PHY Specific Control Register, Address 0x10)                                                                    |    |

| 7.3.4. PHYSR (PHY Specific Status Register, Address 0x11)                                                                     |    |

| 7.3.5. INER (Interrupt Enable Register, Address 0x12)                                                                         |    |

| 7.3.6. INSR (Interrupt Status Register, Address 0x13)                                                                         |    |

| 7.3.7. RXERC (Receive Error Counter, Address 0x15)                                                                            |    |

| 7.3.8. LEDCR (LED Control Register, Address 0x18)                                                                             |    |

| 7.3.9. PAGSEL (Page Select Register, Address 0x1F)                                                                            |    |

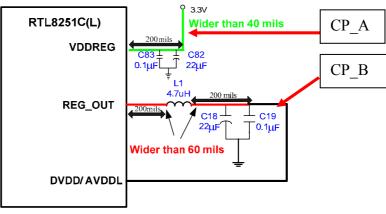

| 8. SWITCHING REGULATOR                                                                                                        |    |

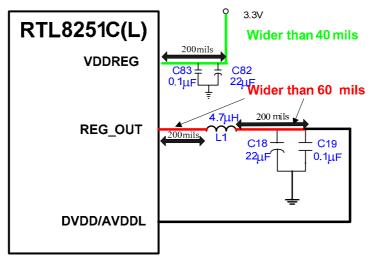

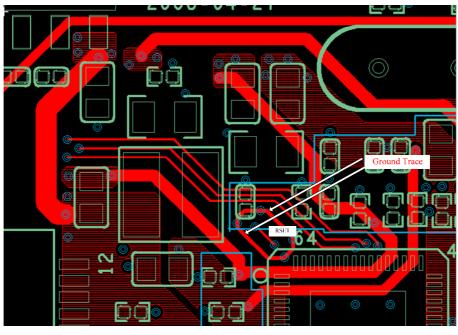

| 8.1. PCB LAYOUT                                                                                                               | 34 |

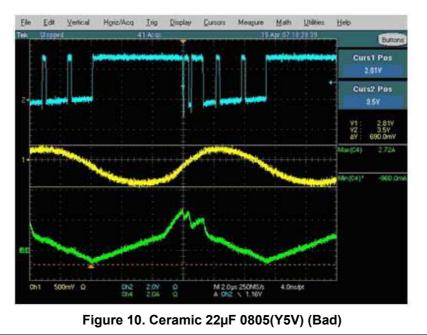

| 8.2. INDUCTOR AND CAPACITOR PARTS LIST                                                                                        |    |

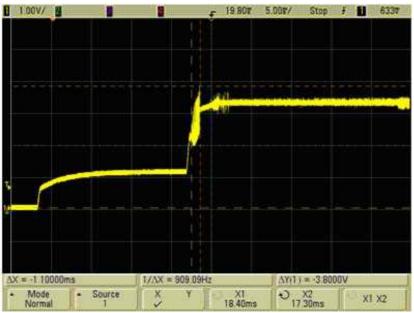

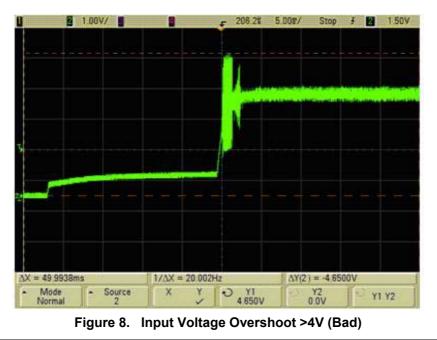

| 8.3. MEASUREMENT CRITERIA                                                                                                     |    |

| 8.4. TYPICAL SWITCHING REGULATOR PCB LAYOUT                                                                                   |    |

| 8.5. EFFICIENCY MEASUREMENT                                                                                                   |    |

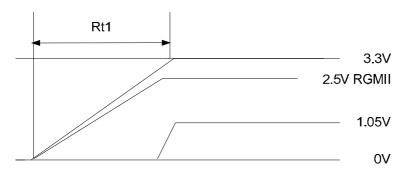

| 8.6. POWER SEQUENCE                                                                                                           |    |

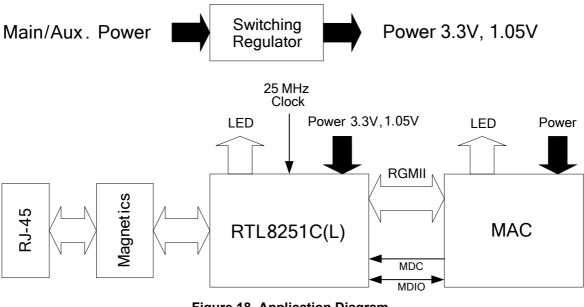

| 9. APPLICATION DIAGRAM                                                                                                        |    |

| 10. CHARACTERISTICS                                                                                                           |    |

| 10.1. Absolute Maximum Ratings                                                                                                | 43 |

| 10.2. RECOMMENDED OPERATING CONDITIONS                                                                                        |    |

| 10.3. CRYSTAL REQUIREMENTS                                                                                                    |    |

| 10.4. DC CHARACTERISTICS                                                                                                      |    |

| 10.5. AC CHARACTERISTICS                                                                                                      |    |

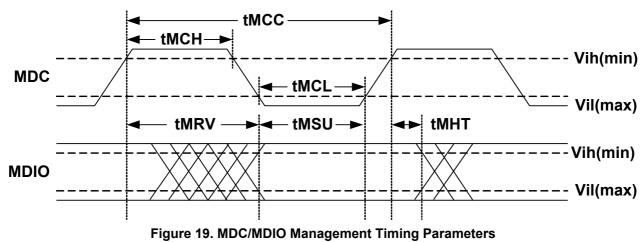

| 10.5.1. MDC/MDIO Timing                                                                                                       |    |

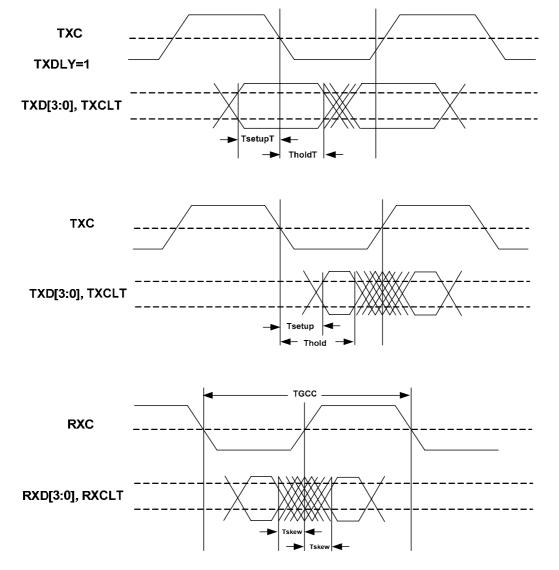

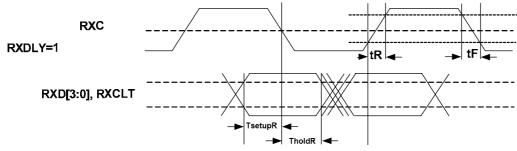

| 10.5.2. RGMII Timing Modes                                                                                                    |    |

| 11. MECHANICAL DIMENSIONS                                                                                                     |    |

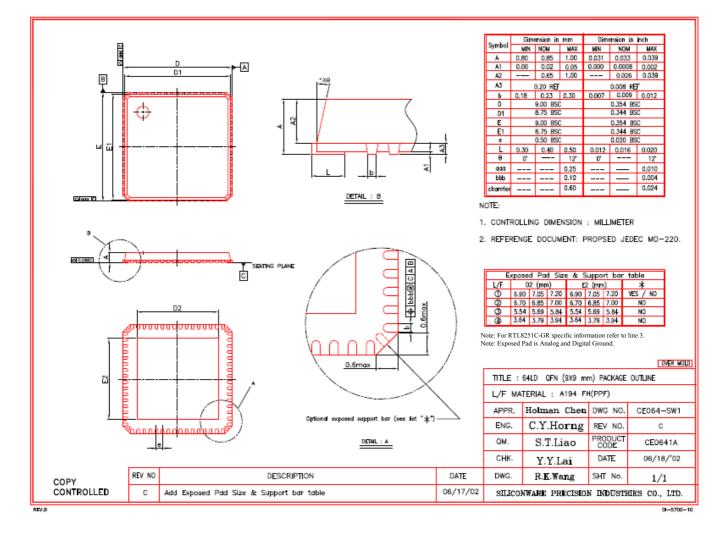

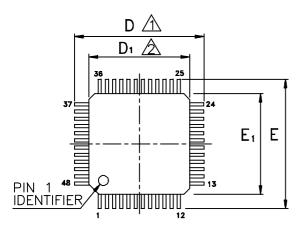

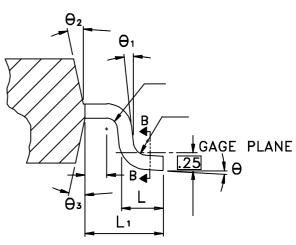

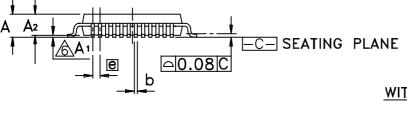

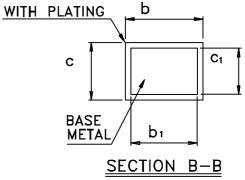

| 11.1. RTL8251C 64-Pin QFN Mechanical Dimensions                                                                               |    |

| 11.1. RTL8251CL 48-Pin LQFP MECHANICAL DIMENSIONS                                                                             |    |

| 11.2.       RTL8251CL 48-PIN LQFP MECHANICAL DIMENSIONS         11.3.       RTL8251CL 48-PIN LQFP MECHANICAL DIMENSIONS NOTES |    |

| 12. ORDERING INFORMATION                                                                                                      |    |

iv

# List of Tables

| TABLE 2.       CLOCK       5         TABLE 3.       GMII       6         TABLE 4.       MANAGEMENT INTERFACE       6         TABLE 5.       REST       6         TABLE 5.       REST       6         TABLE 6.       MODE SELECTION.       7         TABLE 7.       LED INDICATION       7         TABLE 9.       POWER AND REFERENCE       7         TABLE 10.       CONNECTED       8         TABLE 11.       CONFIGURATION REGISTER DEFINITION       10         TABLE 12.       CONFIGURATION REGISTER DEFINITION       10         TABLE 14.       10000BASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS       14         TABLE 15.       TITZSIC LED CONFIGURATION       19         TABLE 14.       1000BASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS       14         TABLE 17.       10       14         TABLE 18.       LED CONFIGURATION       19         TABLE 14.       1000BASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS       20         TABLE 15.       TABLE 14.       1000BASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS       20         TABLE 14.       REGISTER MAPPINO AND DEFINITIONS       20       20         TABLE 12.       REGISTER MAPPINO AND DEFINITIONS       20                                                                                                                                                                                                                                                                                                                                    | TABLE 1.  | TRANSCEIVER INTERFACE                          | 5  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------------|----|

| TABLE 4.       MANAGENEST INTERFACE.       6         TABLE 5.       RESET.       6         TABLE 5.       RESET.       7         TABLE 5.       RESET.       7         TABLE 5.       REGULATOR AND REFERENCE.       7         TABLE 9.       POWER AND GROUND.       8         TABLE 11.       CONFIGURATION REGISTER.       10         TABLE 12.       CONFIGURATION REGISTER.       10         TABLE 13.       TABLE 14.       1000BASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS.       12         TABLE 14.       1000BASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS.       14         TABLE 15.       TLE 20 CONFIGURATION.       19         TABLE 16.       RTL8251C LED CONFIGURATION.       19         TABLE 16.       RTL8251CL LED CONFIGURATION.       20         TABLE 17.       LED INDICATION.       20         TABLE 18.       REGISTER TABLE (RTL8251CL).       20         TABLE 19.       LED CONFIGURATION TABLE (RTL8251CL).       20         TABLE 10.       21       22         TABLE 18.       REGISTER TABLE (RTL8251CL).       20         TABLE 19.       LED CONFIGURATION TABLE (RTL8251CL).       20         TABLE 20.       RABLE (RTL8251CL).       20                                                                                                                                                                                                                                                                                                                                    |           |                                                |    |

| TABLE 5.       RESET.       6         TABLE 5.       RESET.       7         TABLE 6.       MODE SELECTION.       7         TABLE 8.       REGULATOR AND REFERENCE.       7         TABLE 8.       REGULATOR AND REFERENCE.       7         TABLE 10.       NOT CONNECTED.       8         TABLE 11.       CONFIGURATION REGISTER DEFINITION       10         TABLE 12.       CONFIGURATION REGISTER DEFINITION       10         TABLE 13.       TYPICAL MDIO FRAME FORMAT.       12         TABLE 14.       TABLE 15.       RTL8251C LED CONFIGURATION.       14         TABLE 15.       RTL8251C LED CONFIGURATION.       9       14         TABLE 14.       TABLE 16.       RTL8251C LED CONFIGURATION.       20         TABLE 15.       RTL8251C LED CONFIGURATION.       20       20         TABLE 16.       RTL8251CL LED CONFIGURATION.       20       20         TABLE 20.       REGISTER TABLE (RTL8251CL).       20       20         TABLE 20.       REGISTER MAPPING AND DEFENTIONS       22       22         TABLE 20.       REGISTER MAPPING AND DEFENTIONS       22       22         TABLE 20.       REGISTER MAPPING AND DEFENTIONS       22       24         TABLE 20.<                                                                                                                                                                                                                                                                                                                          | TABLE 3.  | RGMII                                          | 6  |

| TABLE 6.       MODE SELECTION.       7         TABLE 7.       LED INDICATION.       7         TABLE 8.       REGULATOR AND REFERENCE       7         TABLE 9.       POWER AND GROUND       8         TABLE 10.       NOT CONNECTED       8         TABLE 11.       CONFIGURATION REGISTER DEFINITION       10         TABLE 13.       TORICO CONNECTED       8         TABLE 14.       IOUOBASE: TB ASE AND NEXT PAGES BIT ASSIGNMENTS.       14         TABLE 15.       TH2521CL LED CONFIGURATION       19         TABLE 16.       RTL8251CL LED CONFIGURATION       20         TABLE 10.       20       20         TABLE 10.       20       20         TABLE 12.       DED CONFIGURATION TABLE (RTL8251CL).       20         TABLE 22.       BUSR (MADE DEFINITIONS       22         TABLE 22.       BUSR (MADE DEFINITIONS       22         TABLE 22.       BUSR (MODE STATUS REGISTER, ADDRESS 0x00)       23         TABLE 22.       BUSR (MODE STATUS REGISTER, ADDRESS 0x00)       25      <                                                                                                                                                                                                                                                                                                                     | TABLE 4.  | MANAGEMENT INTERFACE                           | 6  |

| TABLE 7.       LED INDICATION.       7         TABLE 8.       REGULATCA RAD REFERENCE       7         TABLE 9.       POWIE AND GROUND.       8         TABLE 10.       NOT CONNECTED.       8         TABLE 11.       CONFIGURATION REGISTER DEFINITION       10         TABLE 12.       CONFIGURATION REGISTER DEFINITION       10         TABLE 13.       TYPICAL MDIO TRAME FORMAT.       12         TABLE 14.       DOMBASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS.       14         TABLE 15.       RTL 8251C LED CONFIGURATION.       19         TABLE 14.       DOMBASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS.       20         TABLE 15.       RTL 8251C LED CONFIGURATION.       20         TABLE 16.       RTL 8251C L.       20         TABLE 18.       LED INDICATION.       20         TABLE 18.       DED INDICATION.       20         TABLE 21.       BMCR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)       22         TABLE 22.       CONFIGURATION AND DEFINITIONS       22         TABLE 23.       PHYID1 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x01)       24         TABLE 24.       PHYID2 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02)       25         TABLE 24.       ADREX 000TATION LINK PARTINER ABILTY REGISTER, ADDRESS 0x04)                                                                                                                                                                                                                                                           | TABLE 5.  | RESET                                          | 6  |

| TABLE 8. REGULATOR AND REFERENCE.       7         TABLE 9. POWER AND GROUND       8         TABLE 10. NOT CONNECTED       8         TABLE 11. CONFIG PINS VS. CONFIGURATION REGISTER.       10         TABLE 12. CONFIGURATION REGISTER DERIVITION       10         TABLE 13. TYPICAL MDIO FRAME FORMAT.       12         TABLE 14. 1000BASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS.       14         TABLE 15. CONFIGURATION REGISTER DERIVITION       19         TABLE 14. 1122SITC LED CONFIGURATION       19         TABLE 16. RTL&2SITC LED CONFIGURATION       20         TABLE 16. REGISTER TABLE (RTL&2SITCL).       20         TABLE 19. LED CONFIGURATION AND DERINITONS       22         TABLE 20. REGISTER MAPPING AND DERINITONS       22         TABLE 21. BMCR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)       23         TABLE 22. BMSR (BASIC MODE CONTROL REGISTER, ADDRESS 0x01)       24         TABLE 22. BMSR (BASIC MODE STATUS REGISTER, ADDRESS 0x02)       25         TABLE 22. BMSR (BASIC MODE STATUS REGISTER, ADDRESS 0x03)       26         TABLE 23. ANAR (AUTO-NEGOTIATION NEXT PAGE       20         TABLE 24. PHYLD2 (PHY DENTIFIER REGISTER, ADDRESS 0x03)       26         TABLE 25. ANAR (AUTO-NEGOTIATION NEXT PAGE       20         TABLE 26. ANLPAR (AUTO-NEGOTIATION NEXT PAGE REGISTER, ADDRESS 0x05)       27                                                                                                                                                      | TABLE 6.  | MODE SELECTION                                 | 7  |

| TABLE 9.POWER AND GROUND.8TABLE 10. NOT CONFICTED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TABLE 7.  | LED INDICATION                                 | 7  |

| TABLE 10. NOT CONNECTED.8TABLE 11. CONFIG PINS VS. CONFIGURATION REGISTER.10TABLE 12. CONFIGURATION REGISTER DEFINITION10TABLE 13. TYPICAL MDIO FRAME FORMAT.12TABLE 14. 1000BASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS.14TABLE 15. RTIL 8251C LED CONFIGURATION19TABLE 16. RTIL 8251C LED CONFIGURATION19TABLE 17. LED INDICATION.20TABLE 18. LED REGISTER TABLE (RTL8251CL).20TABLE 19. LED CONFIGURATION TABLE (RTL8251CL).20TABLE 19. LED CONFIGURATION TABLE (RTL8251CL).20TABLE 20. REGISTER MAPPING AND DEFINITIONS22TABLE 22. BMSR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)23TABLE 22. BMSR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)23TABLE 23. PHYID1 (PHY IDENTFIER REGISTER, ADDRESS 0x01)24TABLE 24. PHYID2 (PHY IDENTFIER REGISTER, ADDRESS 0x02)25TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x03)26TABLE 25. ANAR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x04)26TABLE 26. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x05)27TABLE 27. ANER (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x05)27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x06)28TABLE 29. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 29. ANSPR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 29. OBECR (10000                                                                          | TABLE 8.  | REGULATOR AND REFERENCE                        | 7  |

| TABLE 11. CONFIG PINS VS. CONFIGURATION REGISTER       10         TABLE 12. CONFIGURATION REGISTER DEFINITION       10         TABLE 13. TYPICAL MDIO FRAME FORMAT       12         TABLE 14. 1000BASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS       14         TABLE 15. RTL&251C LED CONFIGURATION       19         TABLE 16. RTL&251C LED CONFIGURATION       19         TABLE 16. RTL&251C LED CONFIGURATION       20         TABLE 18. LED REGISTER TABLE (RTL&251CL)       20         TABLE 19. LED CONFIGURATION TABLE (RTL&251CL)       20         TABLE 20. REGISTER MAPPING AND DEFINITIONS       22         TABLE 21. RURC (BASIC MODE CONTICL REGISTER, ADDRESS 0x00)       23         TABLE 22. BMSR (BASIC MODE STATUS REGISTER, ADDRESS 0x01)       24         TABLE 23. PHYID1 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02)       25         TABLE 24. ANVER (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x03)       26         TABLE 25. ANAR (AUTO-NEGOTIATION LINC PARNER ABILITY REGISTER, ADDRESS 0x05)       27         TABLE 26. ANL PAR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x05)       27         TABLE 27. MNER (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x05)       27         TABLE 24. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x05)       27         TABLE 25. ANNR (R (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)       28                                                                                |           |                                                |    |

| TABLE 12. CONFIGURATION REGISTER DEFINITION10TABLE 12. CONFIGURATION REGISTER DEFINITION12TABLE 13. TYPICAL MDIO FRAME FORMAT12TABLE 14. 1000BASE-T EASE AND NEXT PAGES BIT ASSIGNMENTS.14TABLE 15. RTL 8251C1 LED CONFIGURATION19TABLE 16. RTL 8251C1 LED CONFIGURATION19TABLE 17. LED INDICATION20TABLE 18. LED INDICATION20TABLE 19. LED INDICATION20TABLE 19. LED INDICATION20TABLE 20. REGISTER TABLE (RTL 8251C1)20TABLE 20. REGISTER MAPPINO AND DEFINITIONS22TABLE 21. BMCR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)23TABLE 22. BMSR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)23TABLE 22. BMSR (BASIC MODE CONTROL REGISTER, ADDRESS 0x02)25TABLE 24. PHYID1 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02)25TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x04)26TABLE 26. ANLPAR (AUTO-NEGOTIATION LINK PARTINER ABILITY REGISTER, ADDRESS 0x05)27TABLE 27. ANER (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x05)27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x06)28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x06)28TABLE 29. GNER (1000BASE-T CONTROL REGISTER, ADDRESS 0x06)28TABLE 20. GNECK (1000BASE-T CONTROL REGISTER, ADDRESS 0x07)28TABLE 20. GNECK (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x07)30TABLE 31. GBSR (1000BASE-T CONTROL REGISTER, ADDRESS 0x10)31TABLE 32. GBESR (1000BASE-T CONTR                                                                                                     |           |                                                |    |

| TABLE 13. TYPICAL MDIO FRAME FORMAT.12TABLE 14. 1000BASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS14TABLE 14. TIL2S21C LED CONFIGURATION19TABLE 16. RTL82S1C LED CONFIGURATION19TABLE 16. RTL82S1C LED CONFIGURATION20TABLE 17. LED REGISTER TABLE (RTL8251CL)20TABLE 18. LED REGISTER TABLE (RTL8251CL)20TABLE 19. LED CONFIGURATION TABLE (RTL8251CL)20TABLE 20. REGISTER MAPPING AND DEFINITIONS22TABLE 21. BMCR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)23TABLE 22. BMSR (BASIC MODE STATUS REGISTER, ADDRESS 0x01)24TABLE 23. PHYID1 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02)25TABLE 24. PHYID2 (PHY IDENTIFIER REGISTER 2, ADDRESS 0x03)26TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x04)26TABLE 26. ANLPAR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x05)27TABLE 27. ANER (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x05)27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x05)28TABLE 29. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 29. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 29. GENS (1000BASE-T EXTENSE ADDRESS 0x04)30TABLE 30. GBSR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x06)30TABLE 31. GBSR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x10)31TABLE 32. GBLSR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x10)31TABLE 33. PHYCR (PHY SPECHIC CONTROL REGISTER, ADDRESS 0x11) <t< td=""><td></td><td></td><td></td></t<>           |           |                                                |    |

| TABLE 14. 1000BASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS.14TABLE 15. RTL8251C LED CONFIGURATION19TABLE 16. RTL8251C LED CONFIGURATION20TABLE 17. LED INDICATION20TABLE 18. LED REGISTER TABLE (RTL8251CL)20TABLE 19. ED CONFIGURATION TABLE (RTL8251CL)20TABLE 19. LED CONFIGURATION TABLE (RTL8251CL)20TABLE 20. REGISTER MAPPING AND DEFINITIONS22TABLE 21. BMCR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)23TABLE 23. BMS (BASIC MODE CONTROL REGISTER, ADDRESS 0x01)24TABLE 24. BMS (BASIC MODE STATUS REGISTER, ADDRESS 0x01)24TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x03)26TABLE 26. ANLPAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x04)26TABLE 26. ANLPAR (AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER, ADDRESS 0x05)27TABLE 27. ANER (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x05)27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE REGISTER, ADDRESS 0x06)27TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE REGISTER, ADDRESS 0x06)28TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x06)28TABLE 31. BMSR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x07)28TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x06)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x06)30TABLE 33. PHYCR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 34. RECORCENTER CONTROL REGISTER, ADDRESS 0x11)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x12)33<                                                        |           |                                                |    |

| TABLE 15. RTL8251C LED CONFIGURATION19TABLE 16. RTL8251CL LED CONFIGURATION19TABLE 16. LED INDICATION20TABLE 17. LED INDICATION20TABLE 18. LED REGISTER TABLE (RTL8251CL)20TABLE 19. LED CONFIGURATION TABLE (RTL8251CL)20TABLE 20. REGISTER MAPPING AND DEFINITIONS22TABLE 21. BMCR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)23TABLE 22. BMSR (BASIC MODE STATUS REGISTER, ADDRESS 0x01)24TABLE 23. PHYID1 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02)25TABLE 24. PHYID2 (PHY IDENTIFIER REGISTER 2, ADDRESS 0x03)26TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x03)26TABLE 26. ANLPAR (AUTO-NEGOTIATION NERT PAGE REGISTER, ADDRESS 0x03)26TABLE 27. ANLPAR (AUTO-NEGOTIATION NERT PAGE RECEIVE REGISTER, ADDRESS 0x05)27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x06)27TABLE 29. ANNPTR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x06)28TABLE 29. ANNPTR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x06)29TABLE 31. GBSR (1000BASE-T CONTROL REGISTER, ADDRESS 0x06)29TABLE 31. GBSR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x07)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x07)30TABLE 34. PHYSR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x10)31TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x12)32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x12)33 <tr< td=""><td></td><td></td><td></td></tr<>                        |           |                                                |    |

| TABLE 16RTL8251CL LED CONFIGURATION19TABLE 17. LED INDICATION20TABLE 18. LED REGISTER TABLE (RTL8251CL)20TABLE 19. LED CONFIGURATION TABLE (RTL8251CL)20TABLE 19. LED CONFIGURATION TABLE (RTL8251CL)20TABLE 20. REGISTER MAPPING AND DEFINITIONS22TABLE 21. BMCR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)23TABLE 22. BMSR (BASIC MODE CONTROL REGISTER, ADDRESS 0x01)24TABLE 23. PHYID1 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02)25TABLE 24. PHYID2 (PHY IDENTIFIER REGISTER 2, ADDRESS 0x03)26TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x04)26TABLE 26. ANLPAR (AUTO-NEGOTIATION NAVERTISING REGISTER, ADDRESS 0x04)26TABLE 26. ANLPAR (AUTO-NEGOTIATION NINK PARTNER ABILITY REGISTER, ADDRESS 0x05)27TABLE 27. ANER (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x05)27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE REASTER, ADDRESS 0x06)28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x08)28TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x09)29TABLE 31. GBSR (1000BASE-T TATUS REGISTER, ADDRESS 0x04)30TABLE 32. GBESR (1000BASE-T TATUS REGISTER, ADDRESS 0x04)30TABLE 34. PHYSR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x06)31TABLE 35. INER (INTERRUPT STATUS REGISTER, ADDRESS 0x10)31TABLE 34. PHYSR (REGISTER, ADDRESS 0x15)33TABLE 35. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x15)33TABLE 34. PHYSR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x15)33                                                                 | TABLE 14. | 1000BASE-T BASE AND NEXT PAGES BIT ASSIGNMENTS | 14 |

| TABLE 17. LED INDICATION20TABLE 18. LED REGISTER TABLE (RTL8251CL)20TABLE 19. LED CONFIGURATION TABLE (RTL8251CL)20TABLE 20. REGISTER MAPPING AND DEFINITIONS22TABLE 21. BMCR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)23TABLE 22. BMSR (BASIC MODE STATUS REGISTER, ADDRESS 0x01)24TABLE 23. PHYID1 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02)25TABLE 24. PHYID2 (PHY IDENTIFIER REGISTER 2, ADDRESS 0x02)25TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x04)26TABLE 26. ANLPAR (AUTO-NEGOTIATION INK PARTNER ABLITY REGISTER, ADDRESS 0x05)27TABLE 27. ANER (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x08)29TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x09)29TABLE 31. GBSR (1000BASE-T CONTROL REGISTER, ADDRESS 0x06)30TABLE 32. GBESR (1000BASE-T CONTROL REGISTER, ADDRESS 0x06)30TABLE 34. PHYSR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x06)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x11)31TABLE 35. INER (INTERRUPT STATUS REGISTER, ADDRESS 0x12)32TABLE 34. PHYSR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x15)33TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x16)31TABLE 34. PHYSR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x15)33TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x15)32TABLE 35. INER (INTERRUPT                                                |           |                                                |    |

| TABLE 18. LED REGISTER TABLE (RTL 8251CL).20TABLE 19. LED CONFIGURATION TABLE (RTL 8251CL).20TABLE 20. REGISTER MAPPING AND DEFINITIONS.22TABLE 21. BMCR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00).23TABLE 22. BMSR (BASIC MODE STATUS REGISTER, ADDRESS 0x01).24TABLE 23. PHYID1 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02).25TABLE 24. PHYID2 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02).26TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x04).26TABLE 26. ANLPAR (AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER, ADDRESS 0x05).27TABLE 27. ANER (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x05).27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x06).28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07).28TABLE 20. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x06).29TABLE 30. GBCR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x07).30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x07).30TABLE 33. PHYCR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x07).30TABLE 34. PHYSR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10).31TABLE 35. INSR (INTERRUPT ENABLE REGISTER, ADDRESS 0x12).32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13).32TABLE 37. RXERC (RECIFIC ERGOR COUNTER, ADDRESS 0x13).32TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15).33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15).33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)                    |           |                                                |    |

| TABLE 19. LED CONFIGURATION TABLE (RTL \$251CL)20TABLE 20. REGISTER MAPPING AND DEFINITIONS22TABLE 21. BMCR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)23TABLE 22. BMSR (BASIC MODE STATUS REGISTER, ADDRESS 0x01)24TABLE 23. PHYID1 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02)25TABLE 24. PHYID2 (PHY IDENTIFIER REGISTER 2, ADDRESS 0x03)26TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x04)26TABLE 26. ANLPAR (AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER, ADDRESS 0x05)27TABLE 26. ANLPAR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x06)27TABLE 27. ANER (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x07)28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x07)28TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x06)29TABLE 31. GBSR (1000BASE-T STATUS REGISTER, ADDRESS 0x04)30TABLE 32. GBESR (1000BASE-T STATUS REGISTER, ADDRESS 0x07)30TABLE 33. PHYCR (PHY SPECIFIC STATUS REGISTER, ADDRESS 0x07)31TABLE 34. PHYSR (PHY SPECIFIC STATUS REGISTER, ADDRESS 0x10)31TABLE 35. INER (INTERRUPT STATUS REGISTER, ADDRESS 0x11)31TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x12)32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x13)32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13)32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15)33TABLE 37. RXERC (RECEIVE RADLE REGISTER, ADDRESS 0x13)<                   |           |                                                |    |

| TABLE 20. REGISTER MAPPING AND DEFINITIONS22TABLE 21. BMCR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)23TABLE 22. BMSR (BASIC MODE STATUS REGISTER, ADDRESS 0x01)24TABLE 23. PHYID1 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02)25TABLE 24. PHYID2 (PHY IDENTIFIER REGISTER 2, ADDRESS 0x03)26TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x04)26TABLE 26. ANLPAR (AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER, ADDRESS 0x05)27TABLE 27. ANER (AUTO-NEGOTIATION NEXT PARSION REGISTER, ADDRESS 0x06)27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x07)28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x07)29TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x09)29TABLE 31. GBSR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x06)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x10)31TABLE 33. PHYCR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 34. PHYSR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 35. INER (INTERNUPT STATUS REGISTER, ADDRESS 0x12)32TABLE 36. INSR (INTERNUPT STATUS REGISTER, ADDRESS 0x12)32TABLE 37. NXERC (RECEIVE ERROR COUNTER, ADDRESS 0x12)32TABLE 36. INSR (INTERNUPT STATUS REGISTER, ADDRESS 0x15)33TABLE 37. NXERC (RECEIVE REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER,                    |           |                                                |    |

| TABLE 21. BMCR (BASIC MODE CONTROL REGISTER, ADDRESS 0x00)23TABLE 22. BMSR (BASIC MODE STATUS REGISTER, ADDRESS 0x01)24TABLE 23. PHYID1 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02)25TABLE 24. PHYID2 (PHY IDENTIFIER REGISTER 2, ADDRESS 0x03)26TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x04)26TABLE 26. ANLPAR (AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER, ADDRESS 0x05)27TABLE 27. ANER (AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER, ADDRESS 0x05)27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x07)28TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x06)29TABLE 31. GBSR (1000BASE-T STATUS REGISTER, ADDRESS 0x06)30TABLE 32. GBESR (1000BASE-T STATUS REGISTER, ADDRESS 0x06)30TABLE 33. PHYCR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 34. PHYSR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 35. INER (INTERRUPT STATUS REGISTER, ADDRESS 0x11)31TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x15)33TABLE 37. NEXEC (RECEIVE EROR COUNTER, ADDRESS 0x15)33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15)33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35 </td <td></td> <td></td> <td></td> |           |                                                |    |

| TABLE 22. BMSR (BASIC MODE STATUS REGISTER, ADDRESS 0x01)24TABLE 23. PHYID1 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02)25TABLE 24. PHYID2 (PHY IDENTIFIER REGISTER 2, ADDRESS 0x03)26TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x04)26TABLE 26. ANLPAR (AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER, ADDRESS 0x05)27TABLE 27. ANER (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x06)27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x06)28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x08)28TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x04)29TABLE 31. GBSR (1000BASE-T STATUS REGISTER, ADDRESS 0x04)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x06)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x07)31TABLE 34. PHYSR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x10)31TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x11)31TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x13)32TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x13)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15)33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35TABLE 41. POWER SEQUENCE PARAMETER43TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 44. CRYSTAL REQUREMEN                                               |           |                                                |    |

| TABLE 23. PHYID1 (PHY IDENTIFIER REGISTER 1, ADDRESS 0x02)25TABLE 24. PHYID2 (PHY IDENTIFIER REGISTER 2, ADDRESS 0x03)26TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x04)26TABLE 26. ANLPAR (AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER, ADDRESS 0x05)27TABLE 27. ANER (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x06)27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x06)28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x08)28TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x04)30TABLE 31. GBSR (1000BASE-T STATUS REGISTER, ADDRESS 0x04)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x07)30TABLE 33. PHYCR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x04)30TABLE 34. PHYSR (PHY SPECIFIC STATUS REGISTER, ADDRESS 0x10)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x11)31TABLE 36. INSR (INTERRUPT ENABLE REGISTER, ADDRESS 0x12)32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15)33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15)33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS4                                                        |           |                                                |    |

| TABLE 24. PHYID2 (PHY IDENTIFIER REGISTER 2, ADDRESS 0x03)26TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x04)26TABLE 26. ANLPAR (AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER, ADDRESS 0x05)27TABLE 27. ANER (AUTO-NEGOTIATION EXPANSION REGISTER, ADDRESS 0x06)27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE REACE/VE REGISTER, ADDRESS 0x08)28TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x09)29TABLE 31. GBSR (1000BASE-T STATUS REGISTER, ADDRESS 0x04)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x07)30TABLE 34. PHYSR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x11)31TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x12)32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15)33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELEC REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELEC REGISTER, ADDRESS 0x15)33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTICS44TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTIC                                                                          |           |                                                |    |

| TABLE 25. ANAR (AUTO-NEGOTIATION ADVERTISING REGISTER, ADDRESS 0x04)26TABLE 26. ANLPAR (AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER, ADDRESS 0x05)27TABLE 27. ANER (AUTO-NEGOTIATION EXPANSION REGISTER, ADDRESS 0x06)27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x08)28TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x06)29TABLE 31. GBSR (1000BASE-T STATUS REGISTER, ADDRESS 0x04)30TABLE 32. GBESR (1000BASE-T STATUS REGISTER, ADDRESS 0x06)30TABLE 32. GBESR (1000BASE-T STATUS REGISTER, ADDRESS 0x07)30TABLE 33. PHYCR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x11)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x12)32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13)32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15)33TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTES44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS45                                                                                                                                                                                  |           |                                                |    |

| TABLE 26. ANLPAR (AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER, ADDRESS 0x05)27TABLE 27. ANER (AUTO-NEGOTIATION EXPANSION REGISTER, ADDRESS 0x06)27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x08)28TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x09)29TABLE 31. GBSR (1000BASE-T STATUS REGISTER, ADDRESS 0x04)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x04)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x07)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x07)30TABLE 33. PHYCR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 34. PHYSR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x11)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x12)32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13)32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15)33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUR RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTICS44TABLE 45. DC CHARACTERISTICS44TABLE 45. DC CHARACTERISTICS4                                                                                   |           |                                                |    |

| TABLE 27. ANER (AUTO-NEGOTIATION EXPANSION REGISTER, ADDRESS 0x06).27TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07).28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x08)28TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x09).29TABLE 31. GBSR (1000BASE-T STATUS REGISTER, ADDRESS 0x0A).30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x0F).30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x0F).30TABLE 33. PHYCR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10).31TABLE 34. PHYSR (PHY SPECIFIC STATUS REGISTER, ADDRESS 0x10).31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x12).32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13).32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15).33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15).33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15).33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST.35TABLE 41. POWER SEQUENCE PARAMETER.42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS.43TABLE 45. DC CHARACTERISTICS.44TABLE 44. RMDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 45. RCMII TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                |           |                                                |    |

| TABLE 28. ANNPTR (AUTO-NEGOTIATION NEXT PAGE TRANSMIT REGISTER, ADDRESS 0x07)28TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x08)28TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x09)29TABLE 31. GBSR (1000BASE-T STATUS REGISTER, ADDRESS 0x0A)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x0F)30TABLE 33. PHYCR (PHY Specific CONTROL REGISTER, ADDRESS 0x10)31TABLE 34. PHYSR (PHY Specific CONTROL REGISTER, ADDRESS 0x11)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x12)32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13)32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15)33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15)33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTICS44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                              |           |                                                |    |

| TABLE 29. ANNPRR (AUTO-NEGOTIATION NEXT PAGE RECEIVE REGISTER, ADDRESS 0x08)28TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x09)29TABLE 31. GBSR (1000BASE-T STATUS REGISTER, ADDRESS 0x0A)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x0F)30TABLE 33. PHYCR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 34. PHYSR (PHY SPECIFIC STATUS REGISTER, ADDRESS 0x11)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x12)32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13)32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x13)32TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x17)33TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTICS44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                                                |    |

| TABLE 30. GBCR (1000BASE-T CONTROL REGISTER, ADDRESS 0x09)29TABLE 31. GBSR (1000BASE-T STATUS REGISTER, ADDRESS 0x0A)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x0F)30TABLE 33. PHYCR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 34. PHYSR (PHY SPECIFIC STATUS REGISTER, ADDRESS 0x11)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x12)32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13)32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15)33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15)33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTICS44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                                                |    |

| TABLE 31. GBSR (1000BASE-T STATUS REGISTER, ADDRESS 0x0A)30TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x0F)30TABLE 33. PHYCR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 34. PHYSR (PHY SPECIFIC STATUS REGISTER, ADDRESS 0x11)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x12)32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13)32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15)33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x18)33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTICS44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                                |    |

| TABLE 32. GBESR (1000BASE-T EXTENDED STATUS REGISTER, ADDRESS 0x0F)30TABLE 33. PHYCR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 34. PHYSR (PHY SPECIFIC STATUS REGISTER, ADDRESS 0x11)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x12)32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13)32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15)33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x15)33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTICS44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                                |    |

| TABLE 33. PHYCR (PHY SPECIFIC CONTROL REGISTER, ADDRESS 0x10)31TABLE 34. PHYSR (PHY SPECIFIC STATUS REGISTER, ADDRESS 0x11)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x12)32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13)32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15)33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x18)33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS.43TABLE 45. DC CHARACTERISTICS44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                                                |    |

| TABLE 34. PHYSR (PHY SPECIFIC STATUS REGISTER, ADDRESS 0x11)31TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x12)32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13)32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15)33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x15)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x1F)33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS.43TABLE 45. DC CHARACTERISTICS.44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                                                |    |

| TABLE 35. INER (INTERRUPT ENABLE REGISTER, ADDRESS 0x12).32TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13).32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15).33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x18).33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x1F).33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST.35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS.43TABLE 45. DC CHARACTERISTICS.44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS.46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                                                |    |

| TABLE 36. INSR (INTERRUPT STATUS REGISTER, ADDRESS 0x13).32TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15).33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x18).33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x1F).33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST.35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS.43TABLE 45. DC CHARACTERISTICS44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                                                |    |

| TABLE 37. RXERC (RECEIVE ERROR COUNTER, ADDRESS 0x15)33TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x18)33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x1F)33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTICS44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                                                |    |

| TABLE 38. LEDCR (LED CONTROL REGISTER, ADDRESS 0x18).33TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x1F).33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST.35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS.43TABLE 45. DC CHARACTERISTICS44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                                                |    |

| TABLE 39. PAGSEL (PAGE SELECT REGISTER, ADDRESS 0x1F)33TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTICS44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                                                |    |

| TABLE 40. INDUCTOR AND CAPACITOR PARTS LIST.35TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS.43TABLE 45. DC CHARACTERISTICS.44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                                                |    |

| TABLE 41. POWER SEQUENCE PARAMETER42TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTICS44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                                                |    |

| TABLE 42. ABSOLUTE MAXIMUM RATINGS43TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTICS44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                                                |    |

| TABLE 43. RECOMMENDED OPERATING CONDITIONS43TABLE 44. CRYSTAL REQUIREMENTS43TABLE 45. DC CHARACTERISTICS44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |                                                |    |

| TABLE 44. CRYSTAL REQUIREMENTS.43TABLE 45. DC CHARACTERISTICS.44TABLE 46. MDC/MDIO MANAGEMENT TIMING PARAMETERS45TABLE 47. RGMII TIMING PARAMETERS46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                                                |    |

| TABLE 45. DC CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                                                |    |